-

超大规模集成电路 编辑

中文名:超大规模集成电路

外文名:VeryLargeScaleIntegrationCircuit

英文:VLSI

分类:计算机工程

在1920年代,一些发明家试图掌握控制固态二极管中电流的方法,他们的构想在后来的双极性晶体管中得以实现。然而,他们的设想直到第二次世界大战结束之后才得以实现。在战争时期,人们把精力集中在制造雷达这样的军工产品,因此电子工业的发展并不如之后那样迅猛,不过人们对于半导体物理学的了解逐渐增加,制造工艺水平也逐渐提升。战后,许多科学家重新开始从事固态电子器件的研究。1947年,著名的贝尔实验室成功地研制了晶体管。自此,电子学的研究方向从真空管转向到了固态电子器件。

晶体管在当时看来具有小型、高效的特点。1950年代,一些电子工程师希望以晶体管为基础,研制比以前更高级、复杂的电路充满了期待。然而,随着电路复杂程度的提升,技术问题对器件性能的影响逐渐引起了人们的注意。

像计算机主板这样复杂的电路,往往对于响应速度有较高的要求。如果计算机的元件过于庞大,或者不同元件之间的导线太长,电信号就不能够在电路中以足够快的速度传播,这样会造成计算机工作缓慢,效率低下,甚至引起逻辑错误。

1958年,德州仪器的杰克·基尔比找到了上述问题的解决方案。他提出,可以把电路中的所有元件和芯片用同一半导体材料块制成。当时他的同事们正在度假,他们结束度假后,基尔比立即展示了他的新设计。随后,他研制了一个这种新型电路的测试版本。1958年9月,第一个集成电路研制成功。尽管这个集成电路看来还非常粗糙,而且存在一些问题,但集成电路在电子学史上确实是个创新的概念。通过在同一材料块上集成所有元件,并通过上方的金属化层连接各个部分,就不再需要分立的独立元件了,这样,就避免了手工组装元件、导线的步骤。此外,电路的特征尺寸大大降低。随着电子设计自动化的逐步发展,制造工艺中的许多流程可以实现自动化控制。自此,把所有元件集成到单一硅片上的想法得以实现,小规模集成电路(Small Scale Integration, SSI)时代始于1960年代早期,后来历经中规模集成电路(Medium Scale Integration, MSI,1960年晚期)、大规模集成电路和超大规模集成电路(1980年早期)。超大规模集成电路的晶体管数量可以达到10,000个。

集成电路按集成度高低的不同可分为小规模集成电路、中规模集成电路、大规模集成电路、超大规模集成电路、特大规模集成电路和巨大规模集成电路等。

小规模集成电路于1960年出现,在一块硅片上包含10-100个元件或1-10个逻辑门。如 逻辑门和触发器等。如果用小规模数字集成电路(SSI)进行设计组合逻辑电路时,是以门电路作为电路的基本单元,所以逻辑函数的化简应使使用的门电路的数目最少,而且门的输入端数目也最少。

中规模集成电路(Medium Scale Integration:MSI)

1966年出现,在一块硅片上包含100-1000个元件或10-100个逻辑门。如 :集成计时器,寄存器,译码器等。

如果选用中规模集成电路(MSI)设计组合逻辑电路时,则以所用集成电路个数最少,品种最少,同时集成电路间的连线也最少。这往往需将逻辑函数表达式变换成选用电路所要求的表达形式,有时可直接用标准范式。

MSI中规模组合逻辑器件功能虽然比小规模集成电路SSI强,但也不像大规模集成电路LSI那样功能专一化,这些器件产品的品种虽然不少,但也不可能完全符合使用者的要求,这就需要将多片级联以扩展其功能,而且还可以用一些标准的中规模继承组件来实现其它一些组合逻辑电路的设计。用中规模集成组件来进行组合逻辑电路设计时,其方法是选择合适的MSI后,将实际问题转化后的逻辑表达式变换为响应的MSI的表达形式。用MSI设计的组合逻辑电路与用门电路设计的组合逻辑电路相比,不仅体积小,重量较轻,而且提高了工作的可靠性。

中规模数据选择起的级联可扩展其选择数据的路数,其功能扩展不仅可用于组合逻辑电路,而且还可用于时序逻辑电路。在组合逻辑电路中主要有以下应用:

(1)级联扩展,以增加选择的路数、位数,可实现由多位到多位的数据传送;

(2)作逻辑函数发生器,用以实现任意组合逻辑电路的设计。

大规模集成电路(Large Scale Integrated circuits:LSI)

1970年出现,在一块硅片上包含103-105个元件或100-10000个逻辑门。如 :半导体存储器,某些计算机外设。628512,628128(128K)最大容量1G。

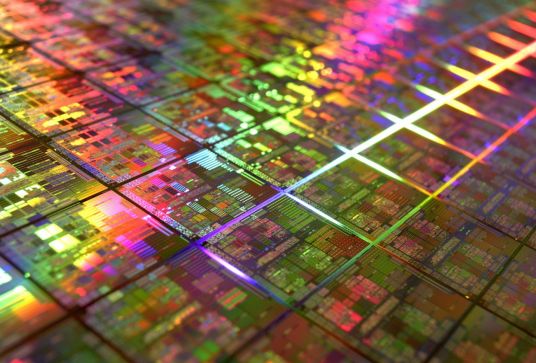

超大规模集成电路(Very Large Scale Integrated circuits:VLSI)

在一块芯片上集成的元件数超过10万个,或门电路数超过万门的集成电路,称为超大规模集成电路。超大规模集成电路是20世纪70年代后期研制成功的,主要用于制造存储器和微处理机。64k位随机存取存储器是第一代超大规模集成电路,大约包含15万个元件,线宽为3微米。

超大规模集成电路的集成度已达到600万个晶体管,线宽达到0.3微米。用超大规模集成电路制造的电子设备,体积小、重量轻、功耗低、可靠性高。利用超大规模集成电路技术可以将一个电子分系统乃至整个电子系统“集成”在一块芯片上,完成信息采集、处理、存储等多种功能。例如,可以将整个386微处理机电路集成在一块芯片上,集成度达250万个晶体管。超大规模集成电路研制成功,是微电子技术的一次飞跃,大大推动了电子技术的进步,从而带动了军事技术和民用技术的发展。超大规模集成电路已成为衡量一个国家科学技术和工业发展水平的重要标志,也是世界主要工业国家,特别是美国和日本竞争最激烈的一个领域。

特大规模集成电路(Ultra Large-Scale Integration:ULSI)

1993年随着集成了1000万个晶体管的16M FLASH和256M DRAM的研制成功,进入了特大规模集成电路ULSI (Ultra Large-Scale Integration)时代。特大规模集成电路的集成组件数在107~109个之间。

ULSI电路集成度的迅速增长主要取决于以下两个因素:一是晶体生长技术已达到极高的水平;二是制造设备不断完善,加工精度、自动化程度和可靠性的提高已使器件尺寸进入深亚微米级领域。硅单晶制备技术可使晶体径向参数均匀,体内微缺陷减少,0.1~0.3um大小的缺陷平均可以少于0.05个/平方厘米。对电路加工过程中诱生的缺陷理论模型也有了较为完整的认识,由此发展了一整套晶体的加工工艺。生产电路用的硅片直径的不断增大,导致生产效率大幅度提高,硅片的直径尺寸已达到12英寸。微缺陷的减少使芯片成品率增加,0.02个/平方厘米缺陷的硅片可使256MB DRAM的成品率达到80~90%。

巨大规模集成电路(Giga Scale Integration:GSI)

1994年由于集成1亿个元件的1G DRAM的研制成功,进入巨大规模集成电路GSI(Giga Scale Integration)时代。巨大规模集成电路的集成组件数在109以上。

截至2012年晚期,数十亿级别的晶体管处理器已经得到商用。随着半导体制造工艺从32纳米水平跃升到下一步22纳米,这种集成电路会更加普遍,尽管会遇到诸如工艺角偏差之类的挑战。值得注意的例子是英伟达的GeForce 700系列的首款显示核心,代号‘GK110’的图形处理器,采用了全部71亿个晶体管来处理数字逻辑。而Itanium的大多数晶体管是用来构成其3千两百万字节的三级缓存。Intel Core i7处理器的芯片集成度达到了14亿个晶体管。所采用的设计与早期不同的是它广泛应用电子设计自动化工具,设计人员可以把大部分精力放在电路逻辑功能的硬件描述语言表达形式,而功能验证、逻辑仿真、逻辑综合、布局、布线、版图等可以由计算机辅助完成。

由于技术规模不断扩大,微处理器的复杂程度也不断提高,微处理器的设计者已经遇到了若干挑战。

1功耗、散热:随着元件集成规模的提升,单位体积产生的热功率也逐渐变大,然而器件散热面积不变,造成单位面积的热耗散达不到要求。同时,单个晶体管微弱亚阈值电流造成的静态功耗由于晶体管数量的大幅增加而变得日益显著。人们提出了一些低功耗设计技术,例如动态电压/频率调节(dynamic voltage and frequency scaling (DVFS)),来降低耗散总功率。

2工艺偏差:由于光刻技术受限于光学规律,更高精确度的掺杂以及刻蚀会变得更加困难,造成误差的可能性会变大。设计者必须在芯片制造前进行技术仿真。

3更严格的设计规律:由于光刻和刻蚀工艺的问题,集成电路布局的设计规则必须更加严格。在设计布局时,设计者必须时刻考虑这些规则。定制设计的总开销已经达到了一个临界点,许多设计机构都倾向于始于电子设计自动化来实现自动设计。

4设计收敛:由于数字电子应用的时钟频率趋于上升,设计者发现要在整个芯片上保持低时钟偏移更加困难。这引发了对于多核心、多处理器架构的兴趣(参见阿姆达尔定律)。

5成本:随着晶粒尺寸的缩小,晶圆尺寸变大,单位晶圆面积上的晶粒数增加,这样制造工艺所用到的光掩模的复杂程度就急剧上升。现代高精度的光掩模技术十分昂贵。